Laporan Akhir Modul 1

1. Jurnal [kembali]

2. Alat dan Bahan [kembali]

3. Rangkaian Simulasi [kembali]

4. Prinsip Kerja [Kembali]

Pada percobaan ini kita menggunakan module D'Lorenzo pada bagian DL2203D dan DL2203C. Pada bagian DL2203D, kita memasukkan logika dari B0 dan B1 yang kemudian dihubungkan ke gerbang logika menggunakan jumper. Logika B0 dan B1 disini kita set sesuai dengan perintah pada modul percobaan,

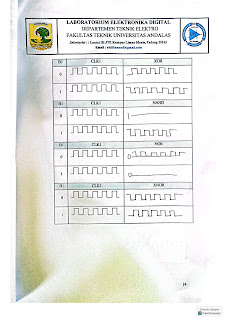

- Gerbang NOT

- Gerbang AND

- Gerbang OR

- Gerbang XOR

- Gerbang NAND

- Gerbang NOR

- Gerbang XNOR

5. Video Rangkaian [kembali]

6. Analisa [kembali]

1.Analisa percobaan output pada tabel pertama percobaan

A. AND

Gerbang AND merupakan gerbang logika menggunakan operasi perkalian. Bisa dilihat diatas bahwa keluaran akan bernilai 1 jika semua nilai input adalah 1, dan jika salah satu atau lebih input ada yang bernilai nol maka output akan bernilai nol,jadi misalnya ada inputan 1 sm 0 di gerbang AND maka output yang akan muncul adalah 0

B.OR

Gerbang OR adalah gerbang logika yang menggunakan operasi penjumlahan. Nilai output bernilai 0 hanya pada jika nilai semua input bernilai 0,misalnya terdapat inputan 0 + 1 pada gerbang OR maka output yang akan dihasilkan adalah 1

C.Not (Inverter)

Gerbang NOT merupakan gerbang di mana keluarannya akan selalu berlawanan dengan masukannya,dengan kata lain gerbang not (inverter) adalah gerbang yang membalikkan hasil input misalnya kita beri input 1 maka hasil yang keluar pada gerbang not adalah 0

D.NOR

Gabungan dari dua gerbang logika yaitu NOT dan OR yang mana hasil dari gerbang OR akan disambungkan ke inverter,jadi misalnya kita beri input 0+1 yang harusnya pada gerbang OR ini bernilai 1 sedangkan pada gerbang NOT adalah 0

E.NAND

Gerbang NAND adalah gerbang AND yang keluarannya disambungkan ke gerbang not. misalnya kita masukan nilai pada gerbang and 0 sm 1 maka hasil yang dikeluarkan pada gerbang NAND adalah 1

F. X-OR

X-OR merupakan gerbang OR yang bersifat exlusif, di mana jika hasil penjumlahan inputnya bernilai ganjil maka outputnya bernilai 1 dan jika hasil penjumlahan inputnya bernilai genap maka outputnya bernilai 0,misalnya kita beri input dengan nilai 0+1 maka outputnya adalah 1

2.Analisa pengaruh clock untuk setiap output pada gerbang logika

ada rangkaian kombinasional, clock tidak memiliki pengaruh terhadap output gerbang logika, bekerja secara langsung berdasarkan input yang masuk. Tidak ada pengaruh dari sinyal clock, karena output bergantung langsung pada nilai input saat itu tanpa adanya elemen penyimpanan atau penundaan waktu.

Tidak ada komentar:

Posting Komentar